May 11

2020

In August 2019, the IBM-initiated OpenPOWER Foundation open sourced the POWER Instruction Set Architecture (ISA), making it a second major open computer architecture after RISC‑V. The decision to open the ISA has created an interesting alternative to proprietary solutions in the server room, especially where security and openness are key, as POWER, with its mainline software support and open firmware approach, had been an established solution in data centers for years. Read more

Dec 11

2019

SAN JOSE, Calif., Dec. 11, 2019 /PRNewswire/ -- QuickLogic Corporation (NASDAQ: QUIK), a developer of ultra-low power multi-core voice-enabled SoCs, embedded FPGA IP, and Endpoint AI solutions, and Antmicro, a high-tech company focusing on introducing open technologies to modern edge computing systems and a RISC‑V ecosystem leader, today announce that Renode, Antmicro's open source functional simulation framework for heterogeneous embedded systems, now has initial support for QuickLogic's EOS™ S3 Sensor Processing Platform. This support enables a more efficient hardware/software co-design approach within a seamless environment, improving time to market, and expanding the potential user base for the EOS S3 SoC. Read more

Oct 28

2019

So far when presenting Renode we mostly focused on using it as a separate tool that provides a closed simulated universe. Read more

Sep 27

2019

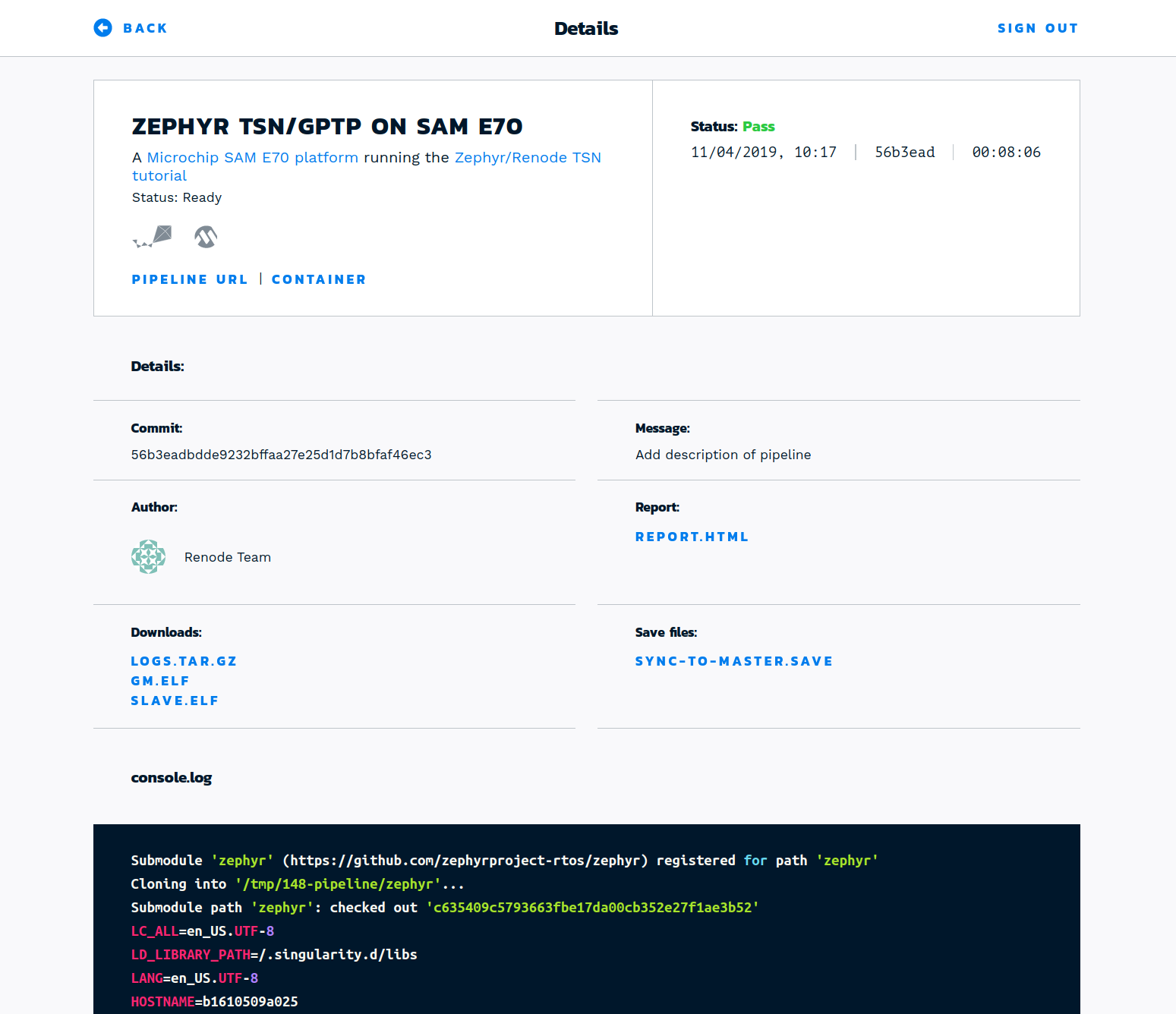

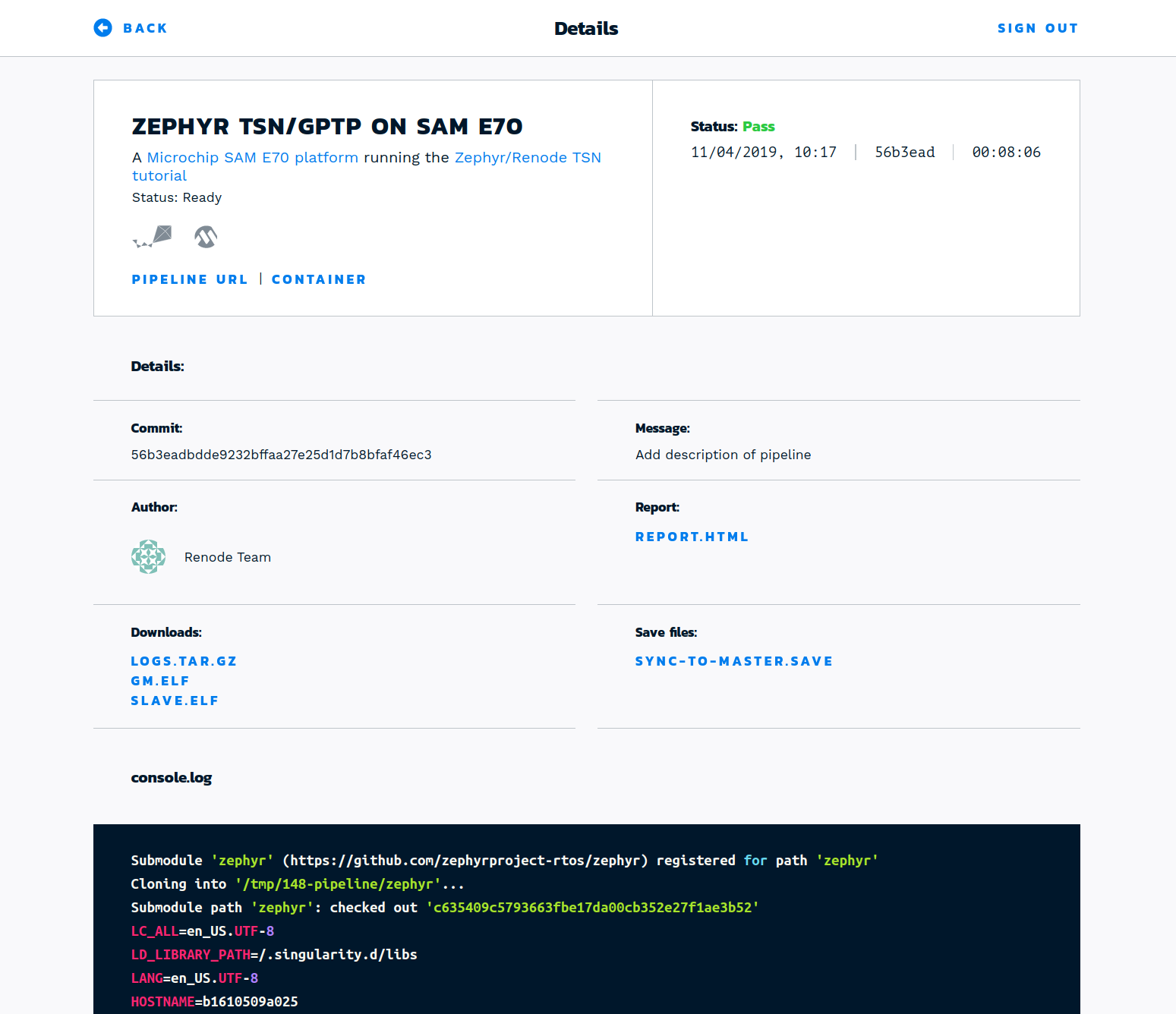

Solving problems that require real-time calculations and precise control typically calls for using an RTOS. While we have been working with a wide variety of RTOSs for various applications (like Contiki-NG for IoT, RTEMS for space applications, eCos for satellite equipment, FreeRTOS in many other fields etc), Antmicro’s RTOS of choice these days has been Zephyr, a Linux-Foundation driven, well-structured, vendor-independent and scalable real-time OS. We’ve ported and adapted Zephyr to many platforms, encouraged its use as a standard on RISC‑V, promoted it in less standard contexts like FPGA devices. Read more

Sep 26

2019

The newest release of Renode, Antmicro’s open source multi-node simulation framework, adds new exciting pieces to your toolbox, along with support for even more RISC‑V platforms and CPUs. Read more