Oct 4

2022

Tracing software execution on real hardware can be challenging, as to access the internal state of the components and the software itself you often need to attach specialized debugging hardware or instrument the source code. Since additional hardware can throw off the timing of events and desynchronize the whole system, and instrumented software may not always be able to use the highest level of compiler optimization, the gathered information may not be the same as for the normal binary. Read more

Sep 2

2022

Note: Since the publication of this article, Renodepedia has been converted into System Designer. Because of that, some of the previous content no longer exists, and so many of the links in this article redirect to the System Designer's landing page. Read more

Sep 2

2022

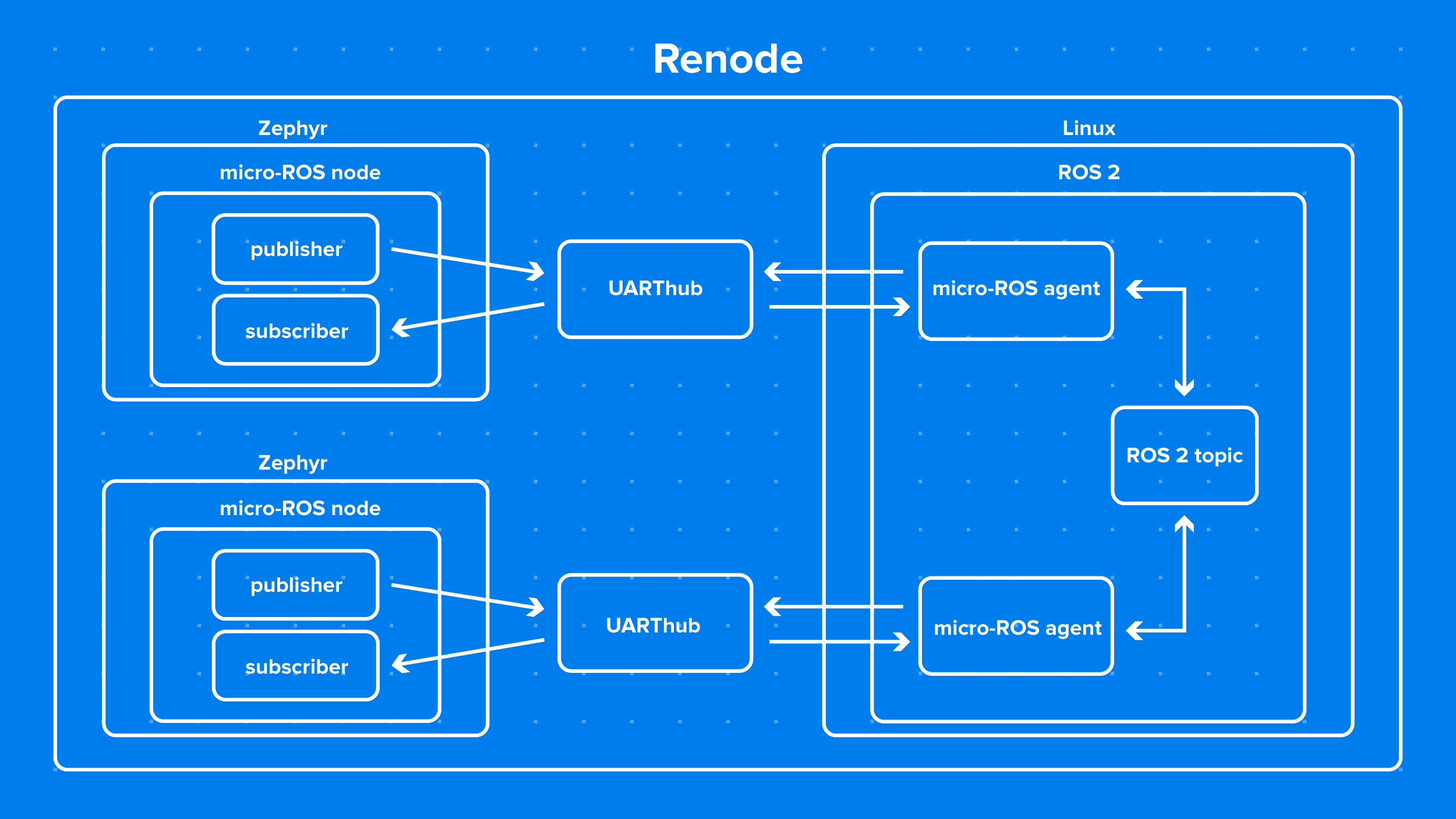

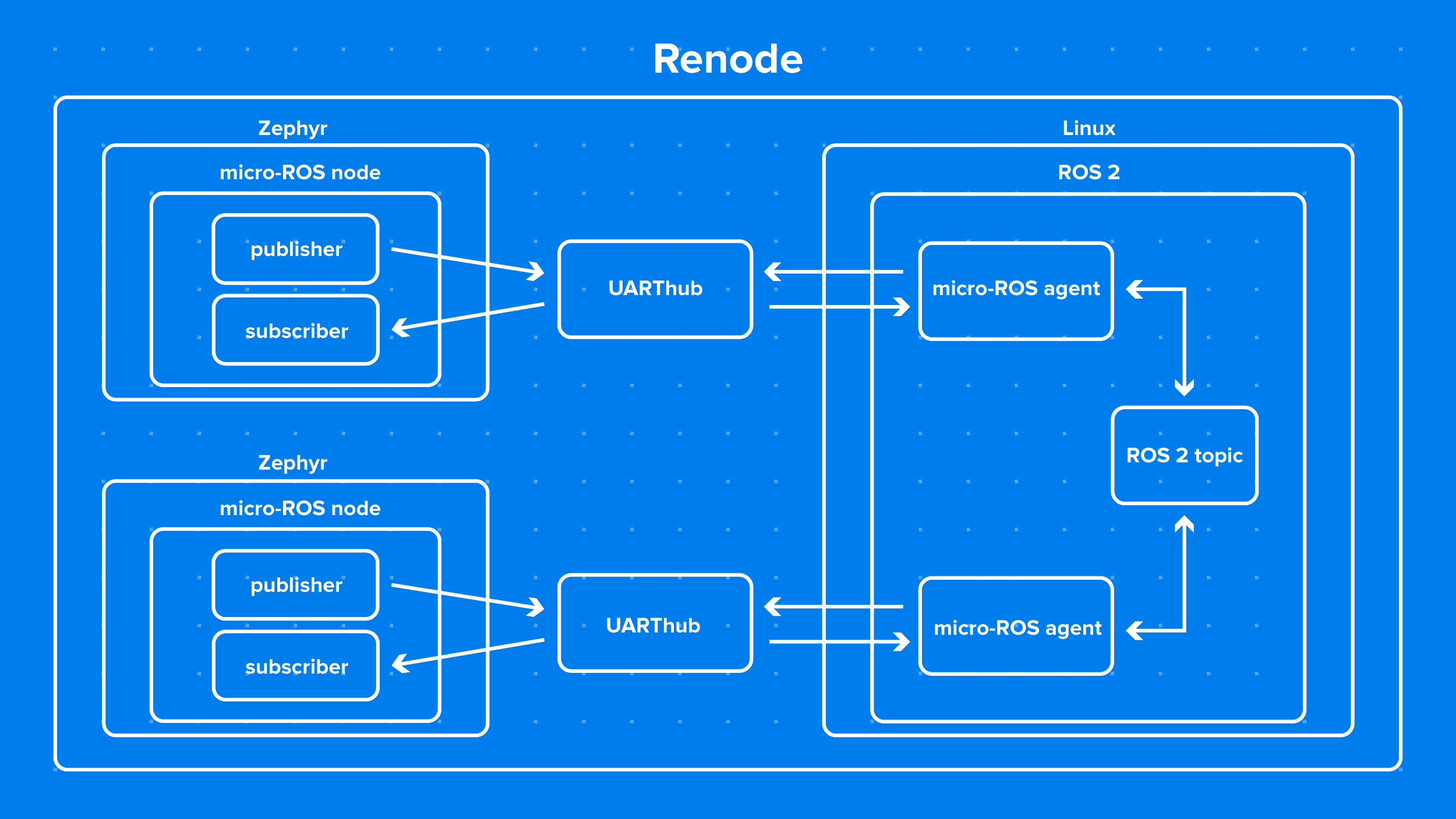

Antmicro assists its customers in developing products using advanced methodologies based on open source tools, and where the relevant tools don’t exist, not shying away from building them. The need to deterministically simulate complex hardware sparked the creation of Renode, the open-source development framework, which can help product development teams implement test-driven workflows throughout all the stages of their product’s lifecycle. Read more

Aug 23

2022

For many years now, Antmicro has been helping its customers build physical device systems based on a wide variety of System-on-Chips. Many of these projects involve the use of the Renode open source framework, which offers a great advantage in product development and testing in all stages of the product life cycle, from pre-silicon prototyping to continuous integration and interop testing in field-deployed devices. Read more

Jul 19

2022

In testing environments, determinism is key - having our application run the exact same way every time regardless of outside influences is crucial to long term stability and trustworthiness of the test suite. That is why Renode, our open source simulation framework, focuses on providing the capability for deterministic testing of hardware systems in software. Read more