May 5

2026

In the last few years, Antmicro has been collaborating with the Google ChromeOS team on simulation-based testing of the ChromiumOS FPMCU (Fingerprint Firmware) module, first by introducing an EC testing suite along with improved support for STM32-based platforms, followed by adding support for the Nuvoton NPCX9 platform in our Renode simulation framework. Read more

Apr 3

2026

Antmicro's Renode simulation framework offers various options for network connectivity, including wired and wireless ones, as well as network traffic inspection via Wireshark integration. So far, Renode has been relying on the TAP interface for connecting to the host network, however, while well supported in Linux, it can't be easily enabled on newer macOS machines. Read more

Mar 6

2026

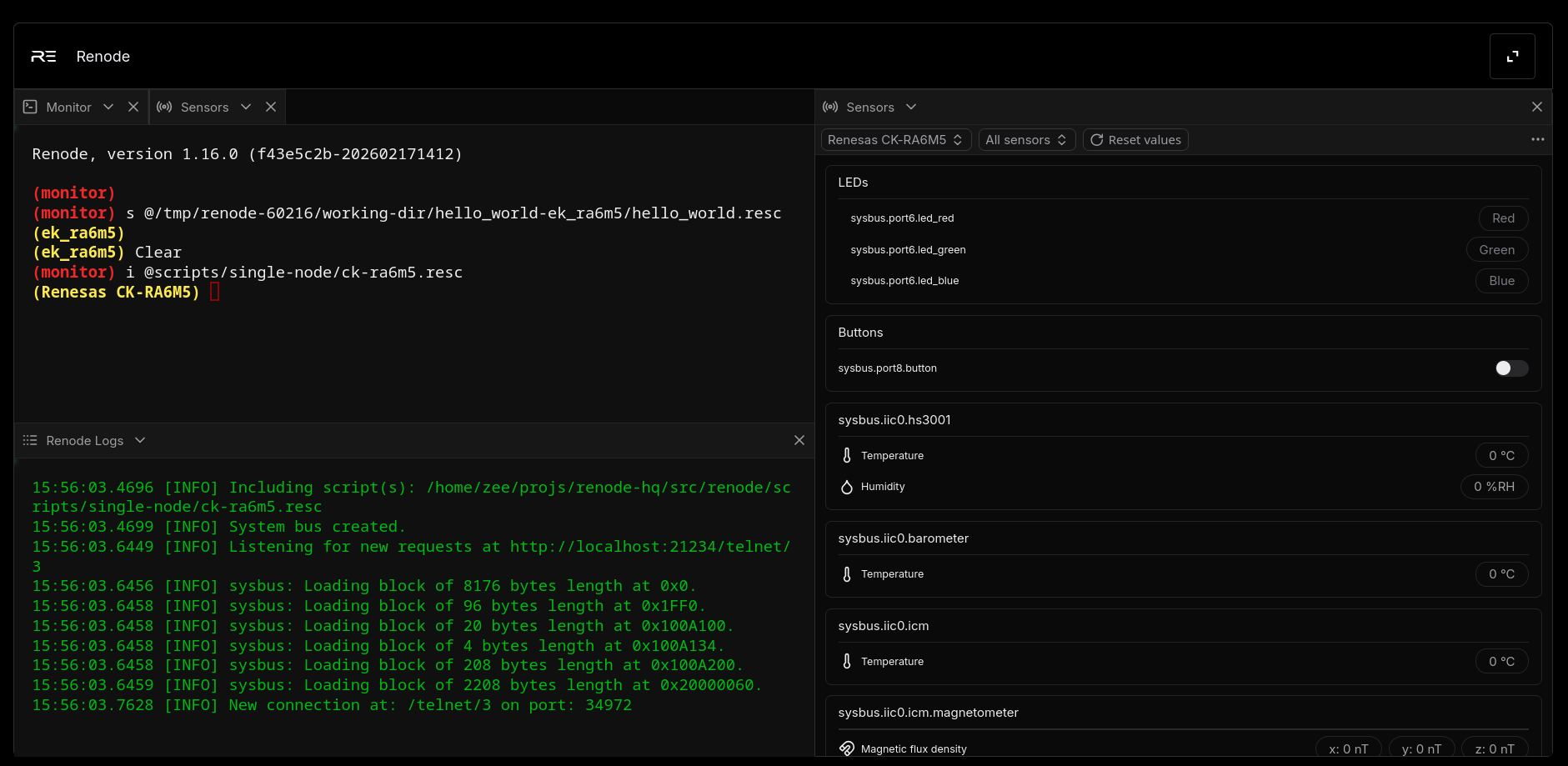

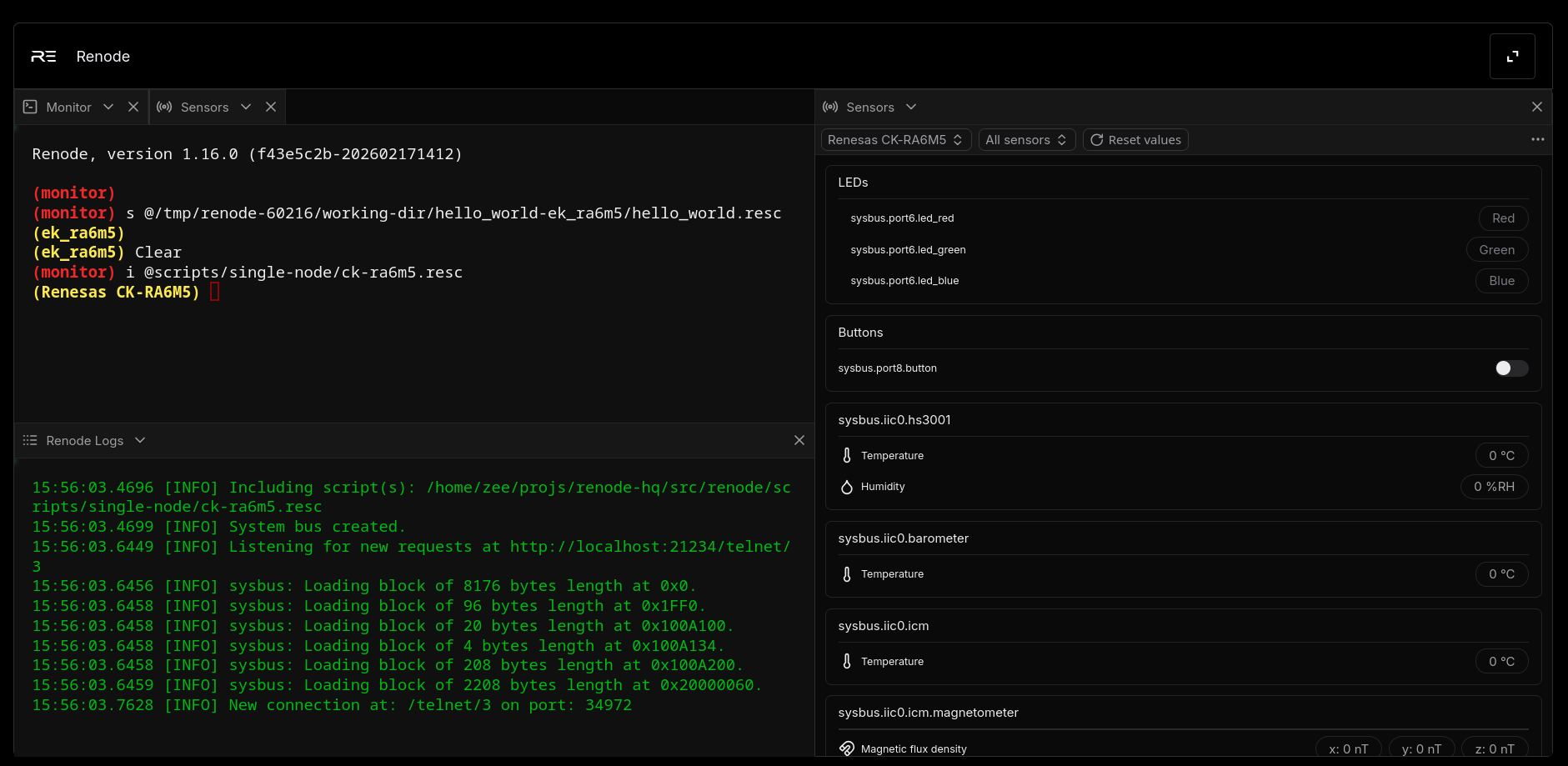

Antmicro's open source Renode simulation framework can be interacted with in many ways: typically, a console-like window, an inline console for headless and remote connections, automated tests via Robot and other systems, as well as a range of various API layers. While a CLI-oriented flow is great for task automation and efficiency, Renode is able to gather insights from the simulation that are better presented in a graphical way. These could potentially include live graphs of input and output values, e.g. sensors, PWM or LEDs, CPU or memory usage inspection, and live execution traces. Read more

Mar 3

2026

A while back, we described our work on implementing and testing Bluetooth communication for an NXP MCU, using Zephyr RTOS and our Renode simulation framework. That setup included an Arm Cortex-M33-based NXP MIMXRT595 MCU designed for use in constrained wireless devices. Read more

Dec 19

2025

Renode allows you to emulate multi-core platforms, executing code on each core in isolation from one another, in parallel. However, in Symmetric Multi-Processing (SMP) architectures, the CPUs can communicate using various mechanisms, e.g. atomic instructions. Renode implements these mechanisms, but the extra synchronization between cores comes at an additional cost in processing time. Read more